| |

|

||||||

|

|

|||||||

|

HioSys PlugInThe I/O-Based Approach - Step by Step

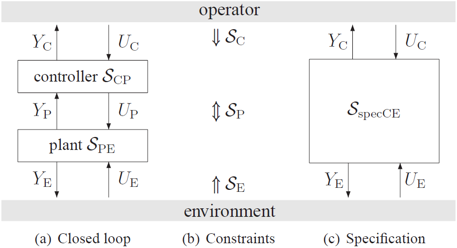

Step 2: Component-Wise Specification and Controller DesignFor each component, if desired, a local I/O controller can be designed according to an individual specification, i.e. at this stage, we face a monolithic controller synthesis problem. The task of the I/O controller is to assist the operator in manipulating the environment according to that specification; see a) and c) in the below figure.

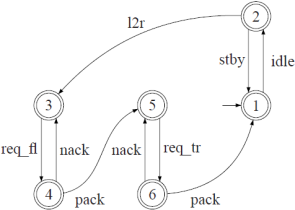

We propose to draft the specification as an I/O-plant model S_specCE = (Sigma_CE,L_CE) of the desired external closed loop, see figure c): by its plant-I/O port (U_C,Y_C) we introduce a set U_C of abstract desired tasks (modes of operation) for the closed loop and a set Y_C of desired responses of the closed loop to the operator. For each task \mu ∈ U_C, the specification expresses the desired effect of the closed loop on the environment by sequences over the (U_E,Y_E)-port and one or more associated responses \nu ∈ Y_C denoting status, failure or completion of the task. To take into account and to exclude misbehaviour by the operator (e.g. tries to trigger a final task before a respective initial task), an operator constraint S_C = (Sigma_C,L_C) can be introduced. The original constraint S_E = (Sigma_E,L_E) for liveness of the plant S_PE may also be assumed for S_specCE such that all in all S_specCE is reasonably designed to be complete and Y_C-live w.r.t. S_C and S_E. Transport Unit.(C++ lua) For the TU, a specification can be designed by the system S_specCE with Sigma_C := U_C∪Y_C = {stby,l2r}∪{idle} and L_specCE as seen in the below Figure.

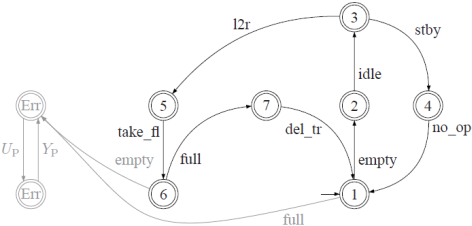

By the measurement event idle we introduce a feedback to the operator notifying that the TU is ready for transport of the next workpiece. We specify that the operator can choose between two operational modes. After the command stby (standby), no interaction with the environment is desired. With the command l2r (left to right) we specify that a workpiece from left is requested from the environment (req_fl). In case of positive acknowledge, the workpiece shall be provided to the right (req_tr). Note that the specification is complete and Y_C-live w.r.t. a minimal S_C and the given S_E, i.e. we allow the operator for arbitrary orders of the commands stby and l2r and may assume the same constraints on the environment as for the original plant. Now, it is the controller's task to enforce appropriate Sigma_P-sequences on the plant to achieve the specified behaviour with respect to the environment. An I/O controller for the single plant component that enforces the specification while guaranteeing the desired liveness properties for the closed loop is conveniently computed using the function HioSynthMonolithic. Note that these guarantees are lost unless the closed loop's surroundings pose a (language) subset of the constraints S_C and S_E. Transport Unit.(C++ lua) For the I/O controller synthesis problem of the TU, our synthesis algorithm returns the controller S_CP as depicted below.

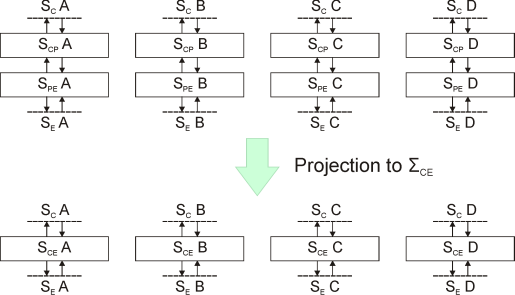

Formally, the I/O controller accepts all measurement events of the plant, even those that can actually not occur; the respective transitions are denoted by gray arrows leading to error states that represent an error behaviour and are never reached. It is verified that if the environment constraint S_E is fulfilled (S_C was chosen minimal), the closed loop is complete and YC-live and features the external behaviour specified by S_specCE. Using Parallel and Project, you can compute the full closed loop S_CPE with L_CPE = L_CP||L_PE and the external closed loop S_CE with L_CE = PCE(L_CPE), e.g. for the TU with index A:

In this simple example, the external closed loop even matches exactly with the specification, which is not the general case. In the tutorial, an identical local controller is designed for all 8 TU's (TU A to TU H). The external closed loop is guaranteed to be an I/O plant. Hence, after the design of local controllers, the overall system is still given as a set of n I/O plants, where the I/O-plant model of a controlled component is given as the external closed loop of the uncontrolled I/O plant and its I/O controller.

libFAUDES 2.33h --- 2025.09.16 --- with "synthesis-omegaaut-observer-diagnosis-iosystem-hiosys-multitasking-coordinationcontrol-timed-iodevice-priorities-simulator-luabindings" |